Catalogue

Buses in Von Neumann Architecture (Unit 5.1)

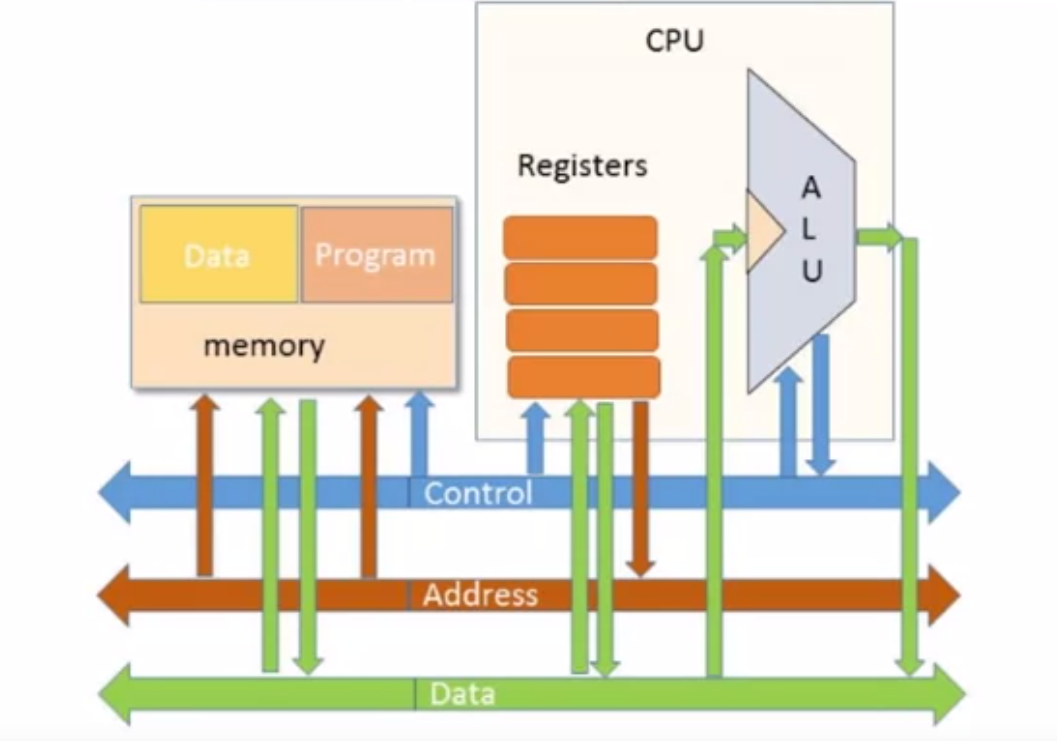

3 Information flows (bus):

The Fetch-Execute Cycle (Unit 5.2)

The basic CPU loop:

- Fetch an Instruction from the Program Memory

- Execute it.

- Repeat this.

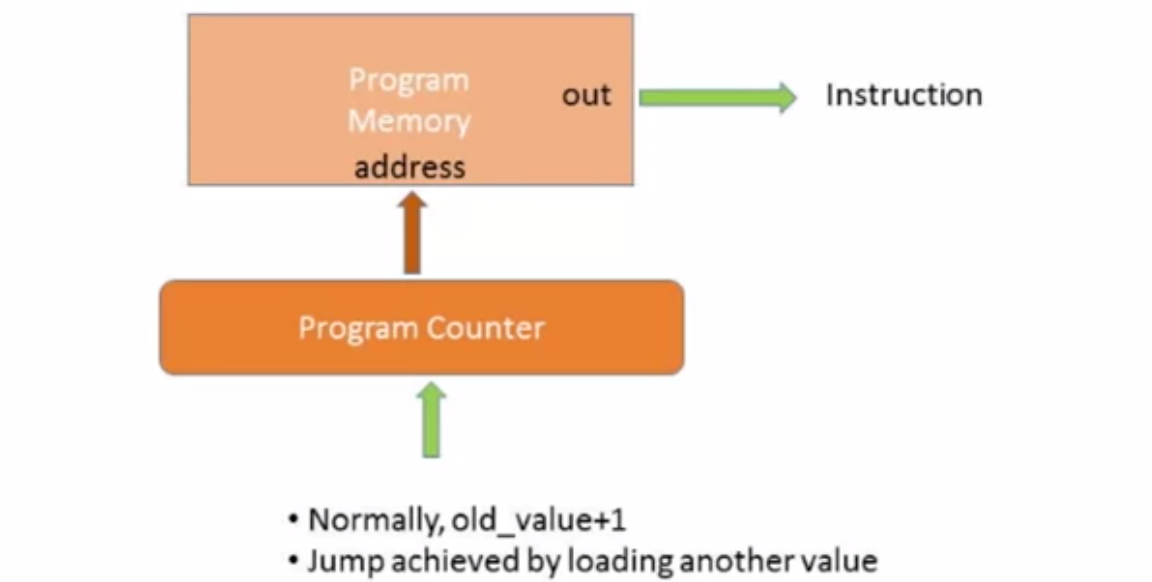

Fetching

- Put the location of the next instruction in the Memory address input (Program Counter)

- Get the instruction code by reading the contents at that Memory location

Program Counter

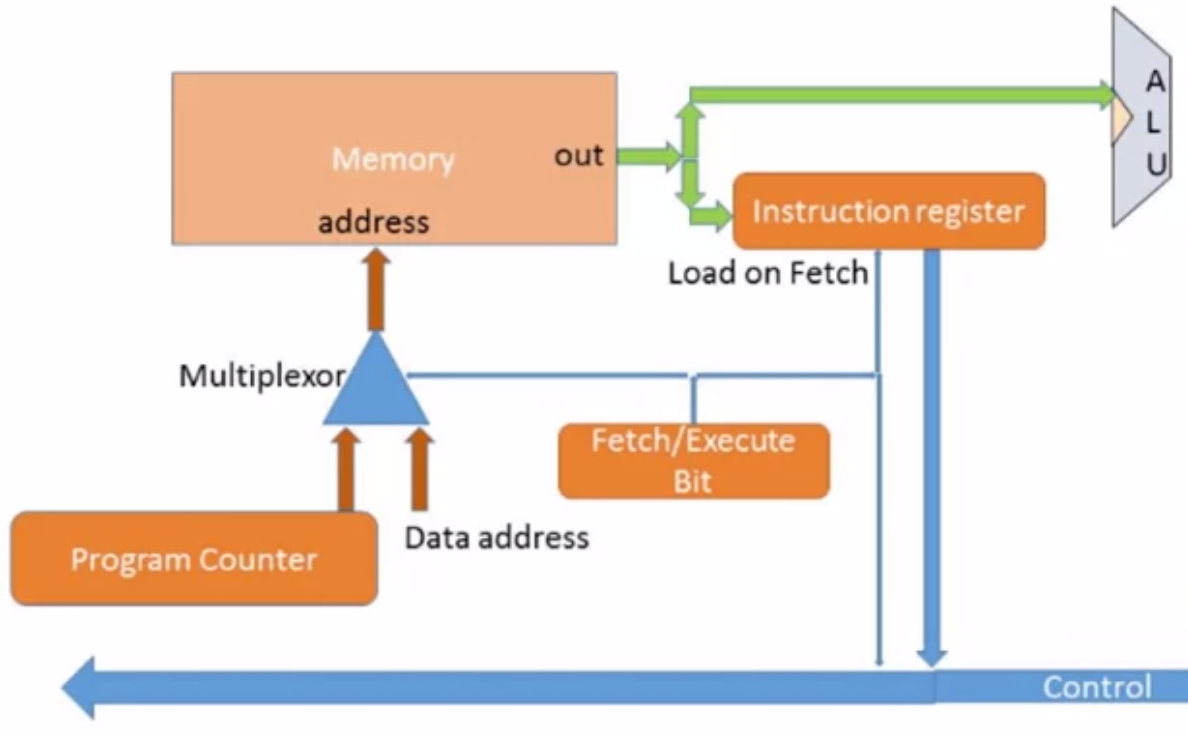

The Fetch-Execute Clash

The instructions and data pieces are stored in a single memory, so there is a clash.

Solution:

Simpler Solution (Harvard Architecture):

To separate the data memory and program memory into 2 modules.

No need to switch between fetching and executing.